notesum.ai

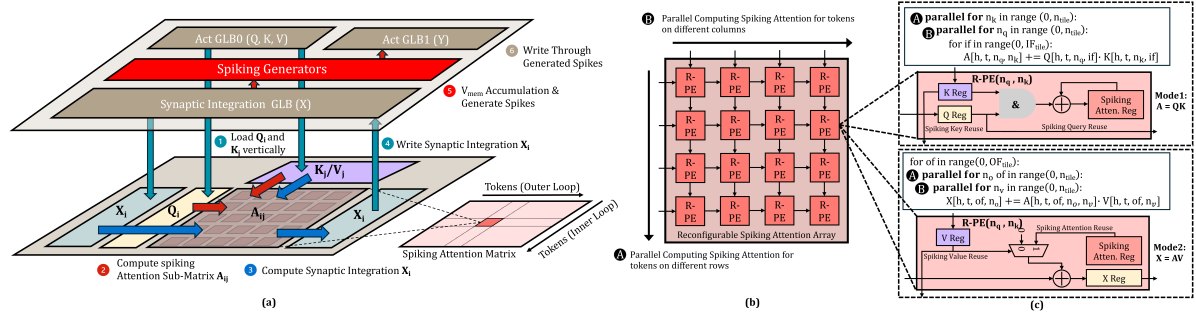

Published at November 11Spiking Transformer Hardware Accelerators in 3D Integration

cs.NE

cs.AR

Released Date: November 11, 2024

Authors: Boxun Xu1, Junyoung Hwang2, Pruek Vanna-iampikul3, Sung Kyu Lim2, Peng Li1

Aff.: 1Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA, USA; 2Department of Electrical and Computer Engineering, Georgia Institute of Technology, GA, USA; 3Department of Electrical and Computer Engineering, Georgia Institute of Technology, GA, USA; Department of Electrical Engineering, Burapha University, Chonburi, Thailand

| Array size HW, weight/synaptic integration bitwidth | , 8b/16b | , 8b/16b | , 4b/12b | |||

| 2D | 3D | 2D | 3D | 2D | 3D | |

| Effective Frequency () | 1.57 | 1.68 | 1.68 | 1.79 | 1.76 | 1.85 |

| Area Footprint () | 0.450.9 | 0.450.45 | 0.450.78 | 0.450.4 | 0.450.78 | 0.450.4 |

| Number of Cells | 152,335 | 152,012 | 88,838 | 88,447 | 83,931 | 83,923 |

| Wire length(m) | 1.37 | 1.10 | 1.17 | 0.99 | 1.00 | 0.81 |

| Internal Power (mW) | 334 | 310 | 221.2 | 215.8 | 201.2 | 186.2 |

| Switching Power (mW) | 152 | 137 | 118.1 | 107.0 | 101.2 | 86.0 |

| Leakage Power (mW) | 30.0 | 29.1 | 22.8 | 21.0 | 19.1 | 14.4 |

| Total Power (mW) | 516 | 476.1 | 362.1 | 343.8 | 321.5 | 286.6 |

| Memory Access Latency (ps) | 82 | 26 | 77 | 19 | 80 | 58 |

| Memory Access Power (mW) | 4.17 | 1.27 | 4.6 | 1.3 | 4.4 | 0.99 |